Le but du décodage d'adresse est de déterminer les combinaisons logiques des fils d'adresse qui permettent d'activer le boîtier mémoire adéquat, en tenant compte bien entendu de la valeur qui y est positionnée . L'exemple qui suit expose une méthodologie simple et efficace pour réaliser un décodage d'adresse.

|

Exemple 3.4.1: |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Le 68000 est un microprocesseur disposant d'un bus d'adresse de 24 bits dont

23 physiquement visibles sur le boîtier (A1-A23), d'un

bus de données de 16 bits et notamment d'une sortie

Le bit A0 qui est interne, participe à la génération des signaux 1. Réaliser le MAP de mémoire et indiquer les adresses de début et de fin de chacune des zones 2. Faire un décodage permettant la sélection de chacune de ces zones, c'est-à-dire chaque boîtier. |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Solution |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

1. MAP mémoire

La zone RAM située en mémoire haute se divise en deux zones de même taille (8K=23x210=213). Mais 14 bits d'adresse (2x8K=24x210=214) sont nécessaires pour adresser toute cette RAM. La RAM2 a donc son adresse de fin égale à (FFFFFF)H, donc son adresse de début égale à (FFFFFF)H-TailleRAM1= (FFE000)H, car sa taille est (1 1111 1111 1111)2=(1FFF)H . La RAM1 a par conséquent son adresse de fin égale à (FFE000)H-1=(FFDFFF)H, d'où son adresse de début ou adresse de base (FFDFFF)H-(001FFF)H= (FFC000)H. 2. Décodage Réaliser le circuit de sélection de chaque boîtier revient à déterminer les bits d'adresse dont les combinaisons vont permettre de sélectionner chaque boîtier. Pour cela on construit une table des adresses comme celle qui suit, connaissant les adresses de début et de fin de chaque zone mémoire.

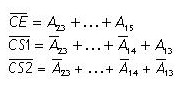

On supprime ensuite les bits d'adresse non indispensables pour la synthèse du circuit de décodage, en procédant comme suit: en commençant par le bit de poids faible A0, on raie les bits qui passe de 0 pour l'adresse de début à 1 pour l'adresse de fin et on s'arrête dès que le bit de début est 1 ou celui de fin est 0 (bits en rouge dans le tableau ci-dessus). Tous les bits d'adresse qui restent sont utiliser pour effectuer un décodage complet. Pour la sélection de la ROM (/CE=0), les bits d'adresse A15 à A23 sont utilisés. Pour la sélection des boîtiers RAM1 (/CS1=0) et RAM2 (/CS2=0), les bits d'adresse à utiliser sont donc A15 à A23:  En prenant en

compte les entrées

La réalisation pratique de ces équations à l'aide de portes logiques s'avère un peu compliquée compte tenu du nombre important d'entrées. C'est pourquoi en pratique on effectue un décodage partiel ou minimal, c'est-à-dire qu'on prend le nombre nécessaire et suffisant de bits permettant de réaliser les circuits de sélection. Dans ce cas de décodage partiel, seul le bit A15 est utile pour la sélection de la ROM et les bits A15 et A13 pour la sélection de la ROM1 et ROM2: quand A15=0 ð zone ROM activée, /CE=0, quand A15=1 ð zone RAM activée et RAM1 activée si en plus A13=0 sinon RAM2, d'où les équations de sélection simplifiées:

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||