Une mémoire est un dispositif permettant d'enregistrer, de stocker ou de restituer des informations (données). Elle peut se résumer en une collection de cases dites cases mémoires. Chaque case mémoire est caractérisée par une adresse et contient une information binaire.

On distingue deux types de mémoires:

![]() les mémoires à accès aléatoire qui se compose de deux classes: les mémoires vives et les mémoires mortes

les mémoires à accès aléatoire qui se compose de deux classes: les mémoires vives et les mémoires mortes

![]() les mémoires à accès séquentiels pour lesquelles l'accès à une case mémoire dépend de sa position et de son adresse: disquette, disque dur, bande magnétique, etc.

les mémoires à accès séquentiels pour lesquelles l'accès à une case mémoire dépend de sa position et de son adresse: disquette, disque dur, bande magnétique, etc.

Dans la suite nous nous intéresserons qu'aux mémoires vives et mortes.

Les mémoires vives appelées communément RAM ( Random Access Memory) sont des mémoires pour lesquelles l'information disparaît lorsqu' elles ne sont plus alimentées. Elles sont lecture, écriture. Elles peuvent être statiques (SRAM) ou dynamiques (DRAM). Dans le cas des RAM statiques, les cellules mémoires sont des bascules bistables qui conservent indéfiniment leur dernier état. Elles n'ont donc pas besoin d'être rafraîchies périodiquement , contrairement aux RAM dynamiques dont chaque cellule mémoire est réalisée autour d'un condensateur.

Les mémoires mortes sont uniquement en lecture. Elles sont appelées communément ROM pour Read Only Memory. L'état logique des différentes cellules mémoires est fixé une fois pour toutes lors de la fabrication. Il existe plusieurs catégories de ROM:

+ PROM (Programmable ROM): les cellules mémoires sont modifiées une seule fois par l'utilisateur.

+ EPROM (Erasable ROM): c'est une PROM effaçable par un rayonnement ultraviolet intense.

+ EEPROM (Electrically EPROM): c'est une ROM programmable et effaçable électriquement par l'utilisateur.

|

Une mémoire est constituée de cellules mémoires (bascules bistables) qui sont regroupées pour former des cases mémoires. Chaque case mémoire est identifiée par une adresse unique obtenue par la combinaison binaire d'un ensemble de fils constituant le bus d'adresse. Cette adresse est généralement exprimée en Hexa. L'ensemble de fils permettant de lire ou d'écrire sur chaque cellule mémoire forme le bus de donnée. Lorsque le bus d'adresse est composé de n fils, la taille de la mémoire est T=2n cases ou mots. Le nombre m de fils du bus de donnée quant à lui indique la largeur des mots mémoires (voir figure ci-contre). |

Une mémoire composée de 210 cases, c'est-à-dire 1024 cases est une mémoire de 1 kilo cases notée 1K cases; celle composée de 220 cases, soit 1024 K cases est notée 1M cases (M pour méga).

La capacité de la mémoire est le nombre de bits qu'elle peut contenir. On l'exprime généralement à l'aide d'un multiple de l'octet (1octet=8bits). Ainsi une mémoire disposant de 23 bits d'adresse et 32 bits de données a une capacité de 223 x 32 = 23 x 220 x 4 x 8 = 64 Mo ( ou 8 M mots de 32 bits) .

|

Les boîtiers mémoires disposent d'un certain nombre de connections externes leur permettant d'être reliés ensemble sur un même bus de donnée et de pouvoir accéder à ce bus indépendamment des autres. L'entrée notée CE (Chip Enable) ou CS (Chip Select), souvent complémentée, permet de déconnecter électroniquement la mémoire du bus de donnée (bus de donnée à l'état haute impédance). L'entrée R/W permet d'autoriser l'écriture ou la lecture de la mémoire. Si

Si

|

Fig. 3.2 Schéma d'un circuit mémoire |

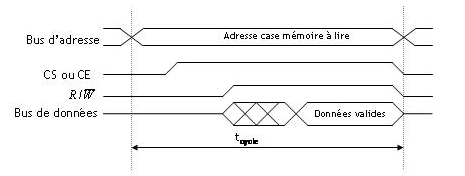

Lire une mémoire consiste à la sélectionner d'abord, placer sur le bus d'adresse les coordonnées de la case mémoire et ensuite transférer son contenu sur le bus de donnée externe (Figure 3.3) .

Fig. 3.3 Chronogramme de lecture d'une mémoire

En pratique les circuits mémoires ont des caractéristiques ne leur permettant pas de satisfaire directement les exigences d'espace mémoires dans les systèmes électroniques. On associe donc différents circuits mémoires afin de remplir ces exigences a savoir augmenter la zone adressable et ou la largeur des mots mémoires. On procède pour cela soit à un agrandissement du bus de données (association parallèle), soit à un agrandissement du bus d'adresse (association série), soit les deux la fois.

3.3.1. Association en parallèleOn effectue une mise en parallèle des blocs mémoires élémentaire afin d'augmenter la largeur des mots, c'est-à-dire la largeur du bus de données, le bus d'adresse commun aux blocs élémentaire restant inchangé. On pourrait par exemple associer en parallèle 4 blocs mémoires de 8 bits pour former un mots mémoires de 32 bits. |

3.3.2. Association en sérieOn effectue une association série des blocs mémoires pour augmenter le nombre de mots mémoires, c'est-à-dire la capacité de la zone adressable. Pour ce faire on augmente la largeur du bus d'adresse. |

|

|

|

|

Exemple 3.3.1: mémoires |

|||||||||||||||||||||||

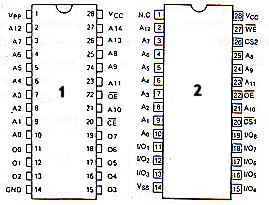

Donner le type et la capacité des mémoires schématisées ci-après:

|

|

||||||||||||||||||||||

|

Solution |

|||||||||||||||||||||||

Il dispose de : - 15 bits d'adresse : A0-A14; - 8 bits de données. Sa capacité est donc: C=2>15x8=2>5x2>10x8=32Ko ou encore 32 Kmots de 8 bits.

- 13 bits d'adresse: A0-A12; - 8 bits de données: I/O1-I/O8, de sorte que sa capacité est C=2>13x8=2>3x2>10x8=8Ko ou 8 Kmots de 8 bits.

|

|||||||||||||||||||||||